# Integrated Systems Design Laboratory

Prof. Deog-Kyoon Jeong (dkjeong@snu.ac.kr)

Department of Electrical and Computer Engineering, Seoul National University, Seoul, Korea

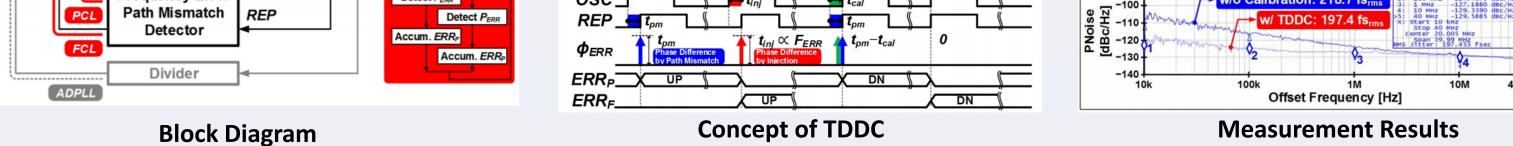

## PDCI (PLL, DLL, CDR, ILO)

### Injection locked- All Digital Phase Locked Loop

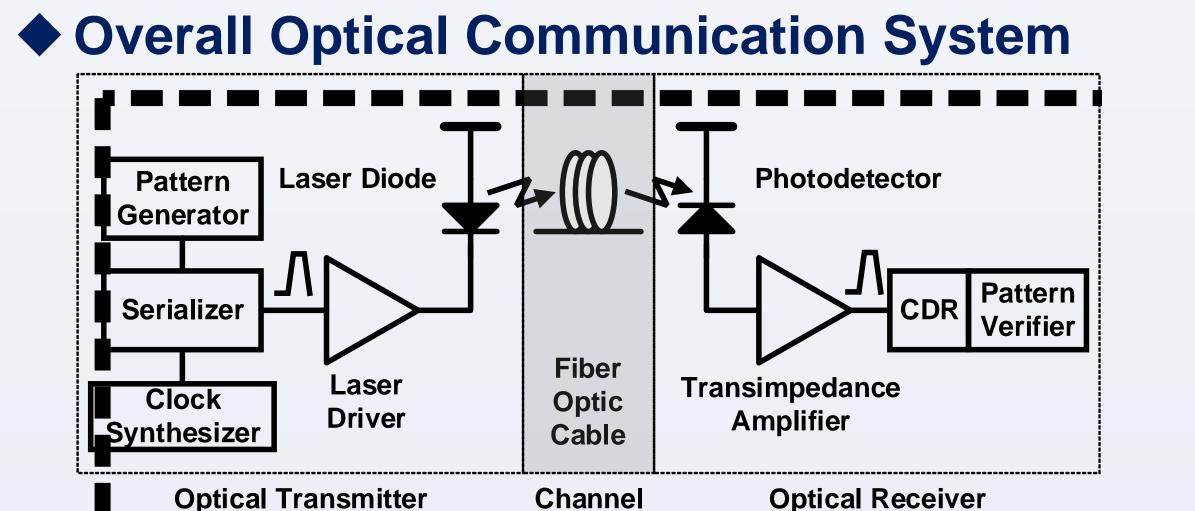

### **Silicon Photonics**

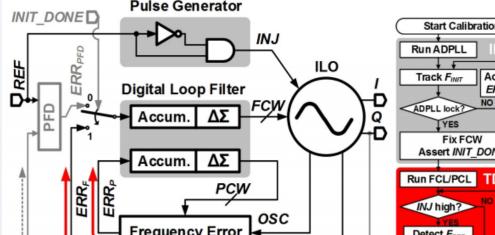

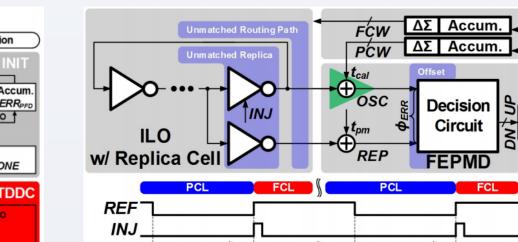

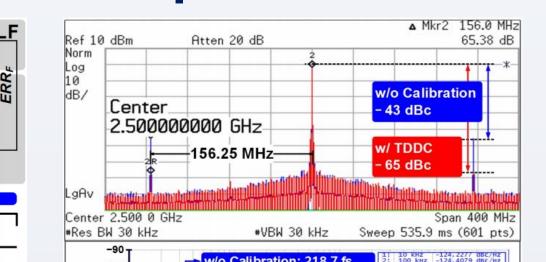

- Low Jitter Injection locked ADPLL

- **Reduction of Reference Spur using Time Division Dual Calibration**

#### Reference-less Clock and Data Recovery

Wide range Single loop Reference-less CDR

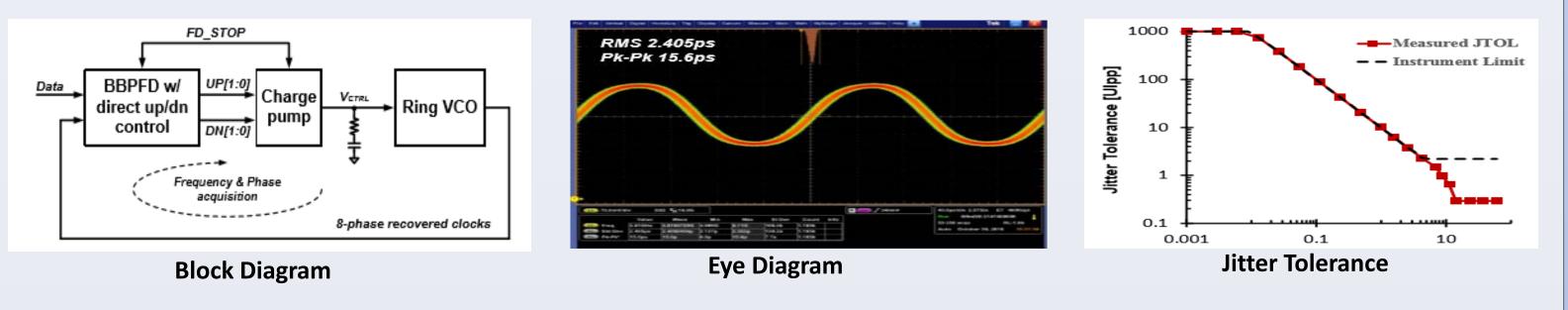

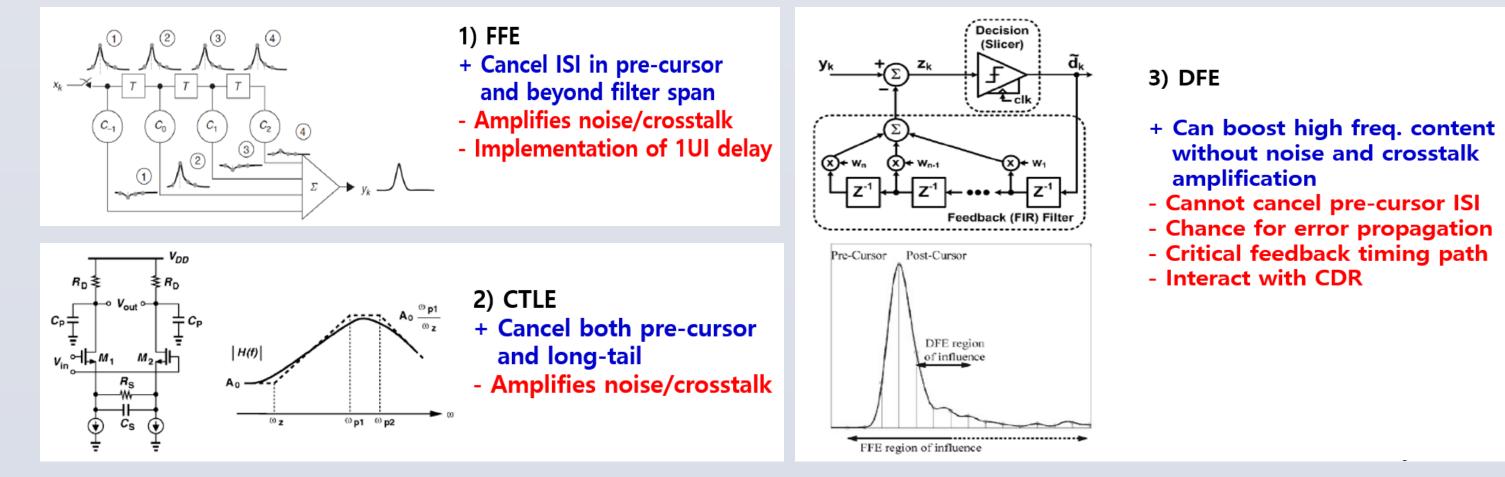

### Equalizer

#### Basic Concept of Equalization

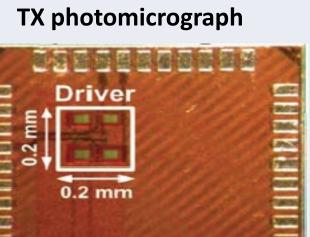

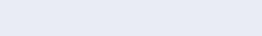

- **CMOS** interface circuits for silicon photonics

- High-voltage, High bandwidth driver

- Low-power, High Speed TIA

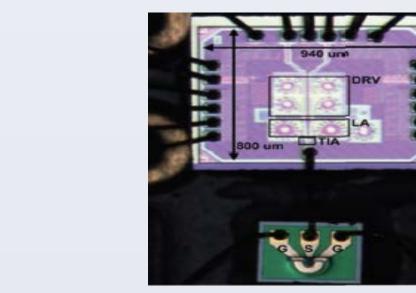

#### TRX Chip & Measurement Eye Diagram

**RX** photomicrograph

**Output Eye Diagram**

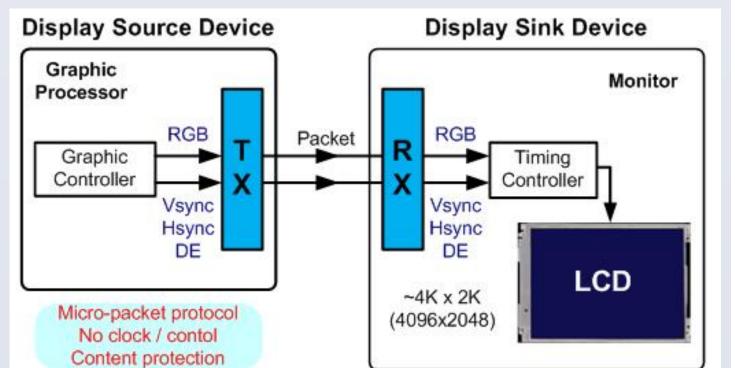

### **Display Port (DP)**

#### Display Port Interface

- **Compensate the channel loss for high-frequency data transmission**

- **Tx Equalizer & Rx Equalizer**

- Maximum Eye-Opening is desired

#### Three Kinds of Equalizer and Characteristics

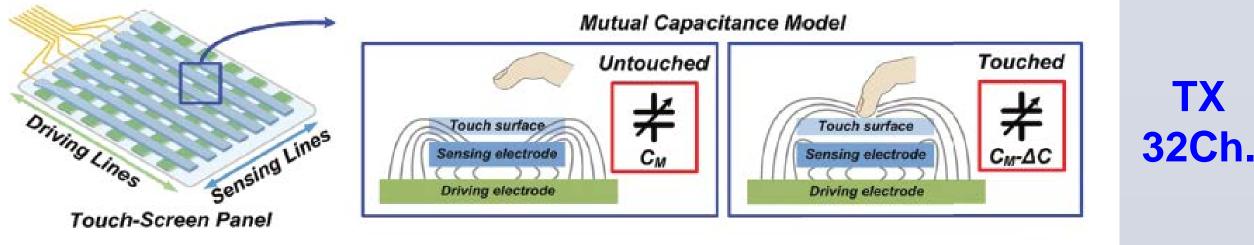

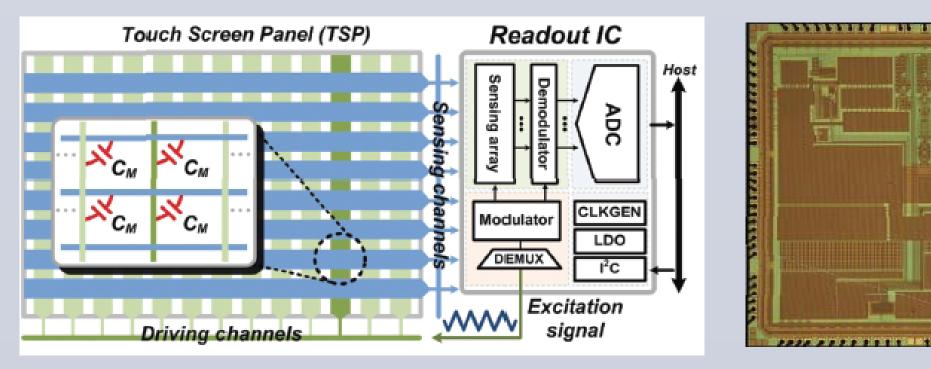

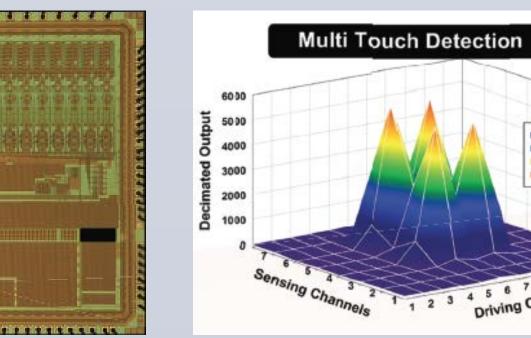

### **Touch Screen Controller (TSC)**

#### Overall System Architecture and Fundamentals

•••

RX

18Ch.

2000

4000

6000

#### **Display Port Data Transport**

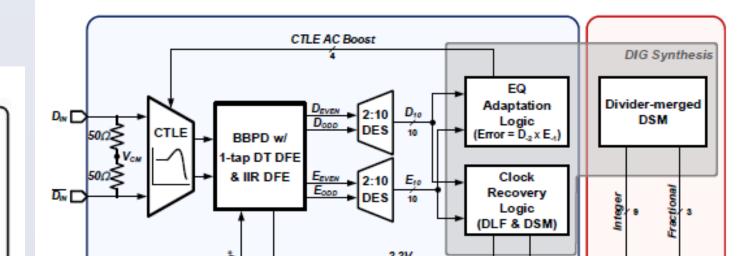

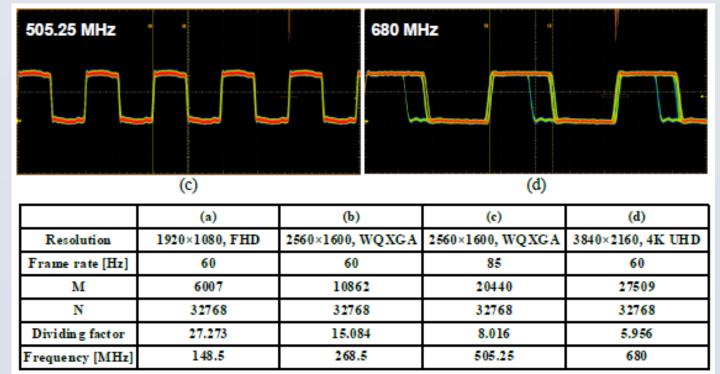

Divider υτ = (M/5N)F UP/DN (Prop. P 8-Phase Clock CDR SCG **Receiver Architecture**

Fractional

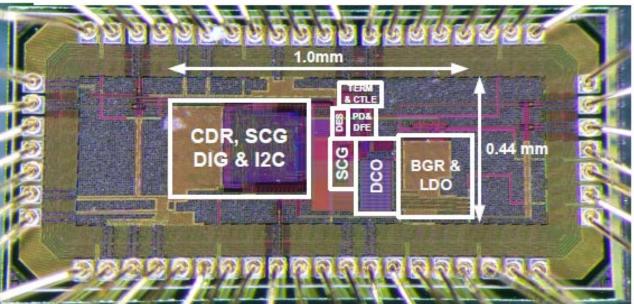

**Chip Photomicrograph**

- Stream clocks of various display resolutions **Display Port supports up to 32.4 Gbps**

- Increased display data due to greater color depth, increased resolutions, and higher refresh rates

- Provides quad full HD (3840X2160) at 120-Hz refresh rates.

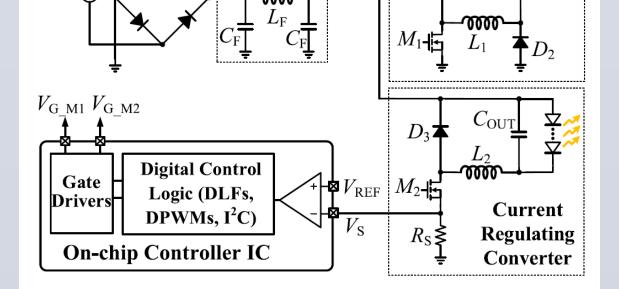

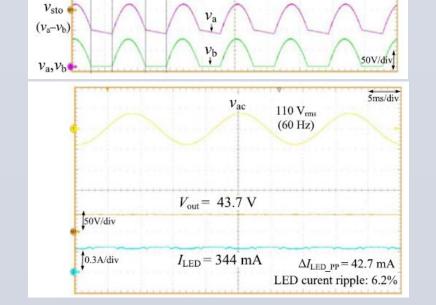

### Power Management IC (PMIC)

### LED Driver

- **Capacitive touch screen panel (TSP) readout IC**

- High SNR and fast scan rate

- High Noise immunity and reconfigurable performance

TX

Loading circuits

\_oading circuits

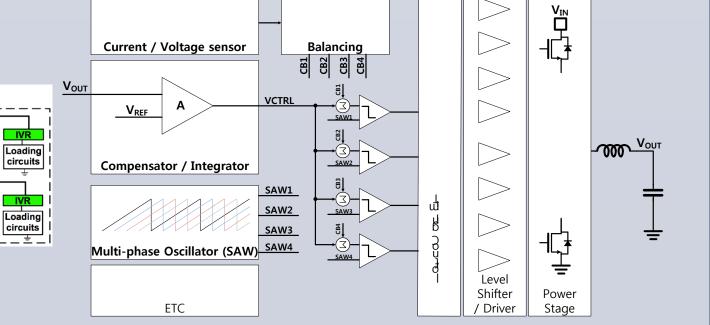

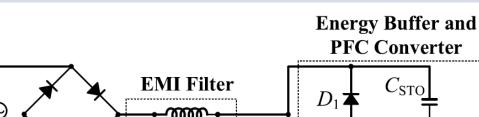

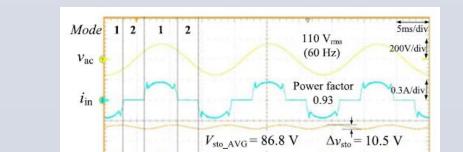

**AC-DC LED Driver topology and controller IC design**

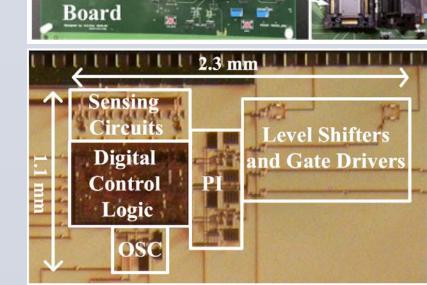

#### Integrated DC-DC converter desi

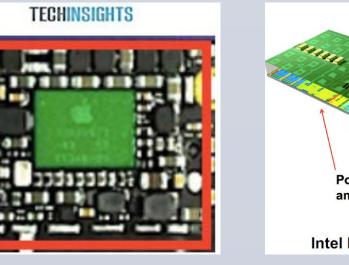

- Power FETs and Contro Intel Haswell, 2013

- **Small passive / Integrated passive elements**

- High frequency controller design