## Analog & Mixed Signal

Suhwan Kim, Ph.D., University of Michigan (EECS) Phone : +82-2-880-9571 Fax : +82-2-871-3284 E-mail : suhwan(at)snu.ac.kr

Electrical Engineering and Computer Science Seoul National University 1 Gwanak-ro, Gwanak-gu, Seoul 08826, Korea

Suhwan Kim received the B.S. and M.S. degrees in Electrical Engineering and Computer Science from Korea University, Seoul Korea, in 1990 and 1992, respectively and the Ph. D. degree in Electrical Engineering and Computer Science from the University of Michigan, Ann Arbor MI, in 2001.

From 1993 to 1999, he was with LG Electronics, Seoul Korea. From 2001 to 2004, he was a Research Staff Member in IBM T. J. Watson Research Center, Yorktown Heights NY. In 2004, Dr. Kim joined Seoul National University, Seoul Korea, where he is currently Professor of Electrical Engineering. His research interests encompass Analog and Mixed-Sig nal Integrated Circuits, High-Speed I/O Circuits, Low-Power Sensor Readout Circuits, and Silicon-Photonics Integrated Circuits. He has received the 1991 Best Student Paper A ward of the IEEE Korea Section and the First Prize (Operational Category) in the VLSI Design Contest of the 2001 ACM/IEEE Design Automation Conference, the Best Paper Aw ard of the 2009 Korean conference on semiconductors, and the 2011 Best Paper Award of the International Symposium on Low-Power Electronics and Design.

He served as a guest editor for IEEE Journal of Solid-State Circuits special issue on IEEE Asian Solid-State Circuits Conference. He has also served as the general co-chair and t echnical program chair for the IEEE International SOC Conference. He has multiple times participated on the technical program committee of the IEEE International SOC Conference, the has multiple times participated on the technical program committee of the IEEE International SOC Conference, the International SOE Conference, the International Symposium on Low-Power Electronics and Design, the IEEE Asian Solid-State Circuits Conference, and the IEEE International Solid-State Circuits Conference, and the IEEE International Solid-State Circuits Conference.

He is a Senior Member of IEEE

## What We've Achieved Until Now!

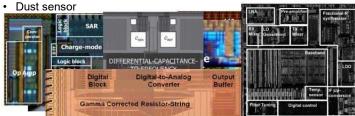

- · CMOS readout IC in a gas sensor

- High accuracy capacitance-to-frequency converter for capacitive sensor

- CMOS capacitance-to-frequency converter for MEMS sensing device

- Delta-Sigma interface circuit with auto-calibrated zero point for c apacitive sensors

- · Charge amplifier for SPM-based data storage

- Low-power time-to-digital converter for biochemical sensor readouts

- · Cyclic time-to-digital converter for capacitive sensor readouts

- High-speed LCD column driver for LCD-TV applications

- 1.9GHz PHS RF transceiver with a 150 kHz low-IF architecture

- Portable ultrasound imaging device

- Automotive electronic control system

- MEMS microphone

- Audio codec

- High-speed pipeline ADC for digital communication and high-qu ality video systems

- · Low-power cyclic ADC for biomedical applications

- High-resolution discrete time delta-sigma (DT-DSM) ADC/DAC for audio and speech recognition applications

- High-resolution continuous time delta-sigma (CT-DSM) ADC for wireless communication applications

- CMOS thermometer for mobile DRAM

- Low-voltage bandgap reference

- 24-bit readout integrated circuit

- Impedance measurement system for health care

- 16-bit ambient light detection system

- Proximity sensor system

Force sensor system

- Optical SpO<sub>2</sub> measurement system

Automotive lidar system

- SAR (Specific Absorption Rate) sensor system

- Referenceless clock data recovery circuit for optically controlled neural interface system

- Impedance-matched bi-direction multi-drop 4.8 Gbps memory controller transceiver

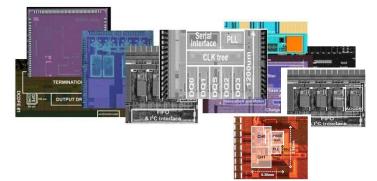

- · High-speed 20 Gbps multi-channel serial interface

- Phase rotator for a 3.75-6.9 Gb/s serial-link receiver

- 1.0-4.0 Gb/s all-digital CDR with 1.0-ps resolution DCO and a daptive proportional gain control

- 0.3-1.4 GHz all-digital fractional-N PLL with adaptive loop gain controller

- Fast-locking CDR circuit with autonomously reconfigurable mechanism

- · 5 Gb/s DFE receiver for seral communications

- All-digital phase-locked loop and clock data recovery for high-sp eed I/O

- Many commercial standard PHY circuits (USB3.0 / HDMI2.0 / LPDDR4)

- Managed DRAM solution

- T-Con PHY for intra-panel interface

- Memory interface for DDR5 / LPDDR5 / HBM3

- Multi-level signaling (Duobinary / PAM4)